# **DEPEND 2011**

The Fourth International Conference on Dependability

ISBN: 978-1-61208-149-6

August 21-27, 2011

Nice/Saint Laurent du Var, France

**DEPEND 2011 Editors**

Pascal Lorenz, University of Haute Alsace, France

Syed Naqvi, CETIC, Belgium

## **DEPEND 2011**

## Foreword

The Fourth International Conference on Dependability (DEPEND 2011), held between August 21-27, 2011 in Nice/Saint Laurent du Var, France, continued a series of special events related to the new challenges in dependability on critical and complex information systems

Most of critical activities in the areas of communications (telephone, Internet), energy & fluids (electricity, gas, water), transportation (railways, airlines, road), life related (health, emergency response, and security), manufacturing (chips, computers, cars) or financial (credit cards, on-line transactions), or refinery& chemical systems rely on networked communication and information systems. Moreover, there are other dedicated systems for data mining, recommenders, sensing, conflict detection, intrusion detection, or maintenance that are complementary to and interact with the former ones.

With large scale and complex systems, their parts expose different static and dynamic features that interact with each others; some systems are more stabile than others, some are more scalable, while others exhibit accurate feedback loops, or are more reliable or fault-tolerant.

Inter-system dependability and intra-system feature dependability require more attention from both theoretical and practical aspects, such as a more formal specification of operational and non-operational requirements, specification of synchronization mechanisms, or dependency exception handing. Considering system and feature dependability becomes crucial for data protection and recoverability when implementing mission critical applications and services.

Static and dynamic dependability, time-oriented, or timeless dependability, dependability perimeter, dependability models, stability and convergence on dependable features and systems, and dependability control and self-management are some of the key topics requiring special treatment. Platforms and tools supporting the dependability requirements are needed.

To deal with dependability, sound methodologies, platforms, and tools are needed to allow system adaptability. The balance dependability/adaptability may determine the life scale of a complex system and settle the right monitoring and control mechanisms. Particular challenging issues pertaining to context-aware, security, mobility, and ubiquity require appropriate mechanisms, methodologies, formalisms, platforms, and tools to support adaptability.

We take here the opportunity to warmly thank all the members of the DEPEND 2011 technical program committee as well as the numerous reviewers. The creation of such a broad and high quality conference program would not have been possible without their involvement. We also kindly thank all the authors that dedicated much of their time and efforts to contribute to the DEPEND 2011. We truly believe that thanks to all these efforts, the final conference program consists of top quality contributions.

This event could also not have been a reality without the support of many individuals, organizations and sponsors. We also gratefully thank the members of the DEPEND 2011 organizing committee for their help in handling the logistics and for their work that is making this professional meeting a success.

We hope the DEPEND 2011 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the area of dependability.

We hope Côte d'Azur provided a pleasant environment during the conference and everyone saved some time for exploring the Mediterranean Coast.

#### **DEPEND 2011 Chairs**

#### **Advisory Chairs**

Reijo Savola, VTT Technical Research Centre of Finland, Finland Sergio Pozo Hidalgo, University of Seville, Spain Manuel Gil Perez, University of Murcia, Spain Petre Dini, Concordia University, Canada / China Space Agency Center - Beijing, China

#### **Industry Liaison Chairs**

Piyi Yang, Wonders Information Co., Ltd., China Timothy Tsai, Hitachi Global Storage Technologies, USA

Research/Industry Chair Michiaki Tatsubori, IBM Research Tokyo, Japan

Special Area Chairs Cross-layers dependability Szu-Chi Wang, National Ilan University, Taiwan

#### Hardware dependability

Peter Tröger, Hasso Plattner Institute / University of Potsdam, Germany

#### **Empirical assessments**

Marcello Cinque, University of Naples Federico II, Italy

**Security and Trust** Syed Naqvi, CETIC, Belgium

## **DEPEND 2011**

## Committee

### **DEPEND Advisory Chairs**

Reijo Savola, VTT Technical Research Centre of Finland, Finland Sergio Pozo Hidalgo, University of Seville, Spain Manuel Gil Perez, University of Murcia, Spain Petre Dini, Concordia University, Canada / China Space Agency Center - Beijing, China

## **DEPEND 2011 Industry Liaison Chairs**

Piyi Yang, Wonders Information Co., Ltd., China Timothy Tsai, Hitachi Global Storage Technologies, USA

## DEPEND 2011 Research/Industry Chair

Michiaki Tatsubori, IBM Research Tokyo, Japan

## **DEPEND 2011 Special Area Chairs**

#### **Cross-layers dependability**

Szu-Chi Wang, National Ilan University, Taiwan

#### Hardware dependability

Peter Tröger, Hasso Plattner Institute / University of Potsdam, Germany

## **Empirical assessments**

Marcello Cinque, University of Naples Federico II, Italy

#### **Security and Trust**

Syed Naqvi, CETIC, Belgium

## **DEPEND 2011 Technical Program Committee**

Afonso Araújo Neto, University of Coimbra, Portugal José Enrique Armendáriz-Iñigo, Universidad Pública de Navarra, Spain Yudistira Dwi Wardhana Asnar, University of Trento, Italy Steffen Bartsch, TZI - Universität Bremen, Germany Jorge Bernal Bernabé, University of Murcia, Spain Andrey Brito, Universidade Federal de Campina Grande, Brazil Antonio Casimiro Costa, University of Lisbon, Portugal Zhe Chen, Université de Toulouse, France Vicent Cholvi, Universitat Jaume I - Castellón, Spain Marcello Cinque, University of Naples Federico II, Italy Vincenzo De Florio, University of Antwerp, Belgium & IBBT, Belgium

Rubén de Juan Marín, Universidad Politécnica de Valencia, Spain Petre Dini, Concordia University, Canada / China Space Agency Center, China Nicola Dragoni, Technical University of Denmark - Lyngby, Denmark Laila El Aimani, Technicolor, Security & Content Protection Labs., Germany Alexander Felfernig, TU - Graz, Austria Nuno Ferreira Neves, University of Lisbon, Portugal Francesco Flammini, Ansaldo STS, Italy Cristina Gacek, City University London, United Kingdom Yan Gao, Northeastern University, China Manuel Gil Perez, University of Murcia, Spain Karl M. Goeschka, Vienna University of Technology, Austria Michael Grottke, University of Erlangen-Nuremberg, Germany Nils Gruschka, NEC Laboratories Europe - Heidelberg, Germany Bjarne E. Helvik, The Norwegian University of Science and Technology (NTNU) - Trondheim, Norway Michael Hobbs, Deakin University - Geelong, Australia Neminath Hubballi, Indian Institute of Technology Guwahati, India Yoshiaki Kakuda, Hiroshima City University, Japan Seah Boon Keong, MIMOS Berhad, Malaysia Phongphun Kijsanayothin, Naresuan University, Thailand Marc-Olivier Killijian, LAAS-CNRS, France Ezzat Kirmani, St. Cloud State University, USA Dong-Seong Kim, Duke University, USA Pankaj Kohli, D-Crypt Pte. Ltd. - Singapore, Singapore Israel Koren, University of Massachusetts - Amherst, USA Mani Krishna, University of Massachusetts - Amherst, USA Inhwan Lee, Hanyang University - Seoul, Korea Byoungcheon Lee, Joongbu University, Korea Alex M. Li, The George Washington University, USA Luigi Lo Iacono, Europäische Fachhochschule Rhein/Erft (EUFH) - Brühl, Germany Paolo Lollini, Università degli Studi di Firenze, Italy Miroslaw Malek, Humboldt-Universitaet zu Berlin, Germany Rivalino Matias Jr., Federal University of Uberlandia, Brazil Manuel Mazzara, Newcastle University, UK George Mohay, Queensland University of Technology, Australia Francesc D. Muñoz-Escoí, Universitat Politècnica de València, Spain Jogesh K. Muppala, The Hong Kong University of Science and Technology, Hong Kong Jun Na, Northeastern University, China Syed Naqvi, CETIC, Belgium Sarmistha Neogy, Jadavpur University, India Mats Neovius, Åbo Akademi University - Turku, Finland Hong Ong, MIMOS Berhad, Malaysia Aljosa Pasic, ATOS Origin, Spain Sergio Pozo Hidalgo, University of Seville, Spain Wolfgang Pree, University of Salzburg, Austria Thomas Quillinan, Thales Research & Technology, The Netherlands Amir Rajabzadeh, Razi University, Iran Wolfgang Reif, University of Augsburg, Germany Juan Carlos Ruiz, Universidad Politécnica de Valencia, Spain

Felix Salfner, Humboldt-Universität zu Berlin, Germany Petter Sandvik, Åbo Akademi University - Turku, Finland Paul Sant, University of Bedfordshire, UK Reijo Savola, VTT Technical Research Centre of Finland, Finland Dimitrios Serpanos, University of Patras & ISI, Greece Komminist Sisai, Fondazione Bruno Kessler, Italy Kuo-Feng Ssu, National Cheng Kung University - Tainan, Taiwan, Republic of China Vladimir Stantchev, Berlin Institute of Technology, Germany Keisuke Takemori, KDDI R&D Laboratories Inc., Japan Oliver Theel, University Oldenburg, Germany Kishor Trivedi, Duke University - Durham USA Peter Tröger, Hasso Plattner Institute / University of Potsdam, Germany Ian Troxel, SEAKR Engineering, Inc., USA Timothy Tsai, Hitachi Global Storage Technologies, USA Marco Vallini, Politehnico di Torino, Italy Ángel Jesús Varela Vaca, University of Sevilla, Spain Bruno Vavala, University of Lisbon, Portugal Szu-Chi Wang, National Ilan University, Taiwan Hironori Washizaki, Waseda University, Japan Claus Wonnemann, Albert-Ludwigs-Universität Freiburg, Germany Pi Yi Yang, Wonders Information Co., Ltd, China Hee Yong Youn, Sungkyunkwan University, Korea

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| Towards Virtual Fault-based Attacks for Security Validation<br>Regis Leveugle, Mohamed Ben Jrad, and Paolo Maistri                                                              | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| On Time, Conflict, Weighting, and Dependency Aspects of Assessing the Trustworthiness of Digital Records <i>Jianqiang Ma, Habtamu Abie, Torbjorn Skramstad, and Mads Nygard</i> | 7  |

| Specification and Verification of the Triple-Modular Redundancy Fault Tolerant System using CSP <i>Tan Lanfang, Tan Qingping, and Li Jianli</i>                                 | 14 |

| Efficient and scalable steady-state dependability verification<br>Diana El Rabih and Nihal Pekergin                                                                             | 18 |

| A Dependable Microcontroller-based Embedded System<br>Amir Rajabzadeh and Mahdi Vosoughifar                                                                                     | 24 |

| Dependable Ordering Policies for Distributed Consistent Systems<br>Matei Dobrescu, Manuela Stoian, and Cosmin Leoveanu                                                          | 30 |

| Fuzzy Event Assignment for Robust Context-Aware Workflows<br>Hannes Wolf, Jonas Palauro, and Klaus Herrmann                                                                     | 37 |

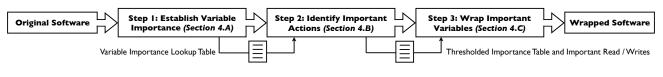

| An Automated Wrapper-based Approach to the Design of Dependable Software<br>Matthew Leeke and Arshad Jhumka                                                                     | 43 |

| An Approach for the Reliability Analysis of Automotive Control Systems<br>Mikhail Glukhikh, Mikhail Moiseev, and Harald Richter                                                 | 51 |

| Methodology and Experience for Designing Safety-Related Systems in IEC 61508<br>Zhe Chen and Gilles Motet                                                                       | 57 |

| Supporting Synthetic Data-Driven Diagnosis through Automated Fault-Injection <i>Patrick E. Lanigan, Thomas E. Fuhrman, and Priya Narasimhan</i>                                 | 65 |

| On Methods for the Formal Specification of Fault Tolerant Systems<br>Manuel Mazzara                                                                                             | 72 |

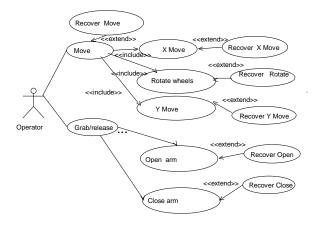

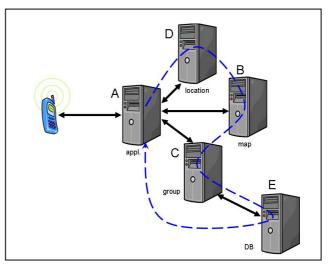

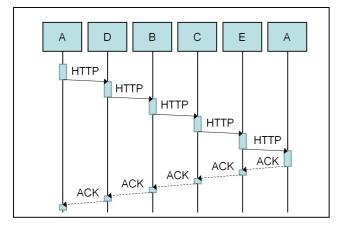

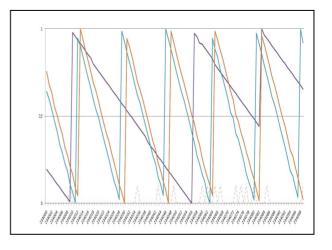

| Failure Modes and Effect Analysis of Use Cases: A Structured Approach to Engineering Fault Tolerance<br>Requirements<br>Elena Troubitsyna                                       | 82 |

| Timing Failures Caused by Resource Starvation in Virtual Machines<br>Sune Jakobsson                                   | 88  |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Video Surveillance in the Cloud: Dependability Analysis<br>Aleksandra Karimaa                                         | 92  |

| Diagnostic Fusion for Dependable Vehicle Architectures<br>Patrick E. Lanigan, Priya Narasimhan, and Thomas E. Fuhrman | 96  |

| Downtime Analysis of Virtual Machine Live Migration<br>Felix Salfner, Peter Troger, and Andreas Polze                 | 100 |

## **Towards Virtual Fault-based Attacks for Security Validation**

R. Leveugle, M. Ben Jrad, P. Maistri TIMA Laboratory Grenoble University (Grenoble INP, UJF, CNRS) 46 Avenue Félix Viallet - 38031 Grenoble Cedex - FRANCE {Regis.Leveugle, Mohamed.Ben-Jrad, Paolo.Maistri}@imag.fr

*Abstract*— Applications increasingly rely on secure embedded systems or "trusted hardware". ASICs (or smart cards) are typically used for high security but SRAM-based FPGAs are also appealing to implement lower-cost and flexible systems. In both cases, designers need a validation of the achieved level of security before they undergo long and costly official security qualification. This paper presents a methodology to accurately evaluate at design time the robustness level with respect to fault-based attacks, without resorting to costly equipments. Practical results are shown. The same methodology can be used in other contexts, for example to evaluate the robustness with respect to particle hits and radiations in spatial or aeronautics electronics although in this case, error models are in general easier to handle.

## *Keywords*— security, dependability, design time robustness evaluation, SRAM-based FPGAs, ASICs

#### I. INTRODUCTION

Embedded hardware-software integrated systems are today the heart of many products. Most application domains are concerned since embedded systems bring new features, added value and competitiveness due to innovation. In many cases, such systems are critical either from a safety or from a security point of view. In both cases, the systems must undergo accurate validations before they are subject to official qualification procedures. In this paper, we will focus on the validations required to guarantee the expected level of robustness with respect to natural or intentional (malicious) perturbations, with a special focus on the later i.e., so-called fault-based attacks.

Due to the overwhelming costs induced by recent technologies, many applications cannot afford developing a specific integrated circuit. They therefore make use of programmable devices (often called FPGAs). For several reasons that will be detailed in the next section, FPGAs configured by uploading data in a volatile memory (SRAM) are very appealing platforms. However, their configuration can easily be perturbed due to the sensitivity of the SRAM to many perturbation sources. When critical functions such as for example crypto-processors are implemented in such a FPGA, it is therefore necessary to analyze and mitigate the effect of errors not only in the user logic and flip-flops but also in the configuration memory.

We will demonstrate in the next sections that under practical attack conditions (using a laser or power glitches) a large number of bits can be simultaneously modified. The most usual error models employed to analyze the effects of natural perturbations (e.g., single bit-flip, or SEU) are therefore not adequate in such situations. Although fault injection techniques can be used to evaluate robustness level and the efficiency of some protection mechanisms [1], the main problem remains the injection of realistic error patterns.

Of course, the best solution to demonstrate the robustness of a given design is to implement it and to put it under real perturbation conditions, for example in a particle accelerator for accelerated testing or under a laser for malicious attacks. However, using such equipments is not always possible due to their availability and to the cost such experiments induce. A new methodology is therefore required in order to reduce the global validation and qualification costs. Our proposal is to use fault injection campaigns as a first validation step, but with accurate error patterns in order to achieve a sufficient precision. These error patterns are first gathered during platform characterizations and can be re-used for several versions of the design, or several designs. The implemented analysis environment is flexible and can mimic different types of error sources. It only requires qualifying a single time the implementation target (e.g., the selected FPGA family) in the considered environments. Our evaluation environment has been implemented for Virtex II/Virtex II Pro devices but can be extended to other FPGAs.

We detail in section II the global context and motivations for this study. Section III summarizes practical results obtained under various attack conditions on several platforms. Section IV presents how such results can be reused to perform accurate and low-cost security evaluations. Some results obtained with the new methodology are then shown in section V.

#### II. CONTEXT AND MOTIVATIONS

As previously mentioned, the behavior of an integrated system can be perturbed in several ways. Natural perturbations can occur for example due to ionizing radiations, particle hits or electromagnetic interferences. Malicious perturbations using for example a laser or voltage glitches can be used to discover secret data stored in a circuit. Such fault-based attacks have become one of the main threats for systems with high security requirements. An early example of fault-based attack is Lenstra's attack on RSA [2], taking advantage of the computations based on the Chinese Remainder Theorem. This attack combines fault injection and crypto-analysis to discover the secret key stored in a circuit. Similar attacks have been published for other types of cryptographic primitives, in particular DES or AES [3, 4]. In the case of malicious perturbations, the errors generated in the circuit are often much more complex than those generated by natural perturbations. We will therefore focus on malicious attacks in this paper, although the presented methodology can also be used in other contexts. We will also focus in the sequel on transient effects i.e., spurious modifications of some data stored in the circuit. Several bits can be simultaneously modified but without damage to the chip; restoring the erroneous data can therefore restart a correct computation.

Secure systems are often implemented in ASICs i.e., circuits specifically manufactured for a given application. In the case of large production volumes, for example for Payper-view television access, specific circuits allow developers to achieve both low cost and maximum protection. However, the development costs induced by recent technologies are quickly increasing and ASICs are no longer affordable for many applications. In most cases, they are replaced by programmable devices (often generically called FPGAs). Among those devices, three main categories exist. Some devices can be programmed only once (e.g., by fuses or antifuses). Once programmed, they are quite close to an ASIC in terms of characteristics. Their main drawbacks are a limited offer and quite high prices. Another device category makes use of non-volatile memories to store the device configuration. The best devices in this category use today Flash memory that is quite robust with respect to perturbations although some critical parts (e.g., control logic) are more sensitive. Such devices are more flexible but slightly less robust than devices based on fuses. Finally, the third category of devices makes use of volatile memory (SRAM) to store the configuration. These devices are less costly than the others and they generally exploit the most advanced technologies. They offer the largest device complexity, so the best integration level. They can easily be reconfigured to add new features or correct some bugs in the system and they often have partial reconfigurability capabilities that can be used to optimize the system implementation and behavior. Specific protections are available to protect the configuration against cloning (e.g., by encrypting it). SRAM-based FPGAs are therefore very appealing for many applications. However, their main drawback is the sensitivity of the configuration SRAM to natural or malicious perturbations. Errors occurring in a SRAM-based FPGA can therefore affect not only the user logic and flip-flops but also the configuration memory. In the first case, the problem is similar to perturbations occurring in an ASIC and modifies either manipulated data or the application control flow. Errors in the configuration memory are in general much more difficult to cope with since several effects can be induced. Manipulated data can be modified, but the function of the circuit can also be changed and will remain erroneous (although the effect is not destructive) until at least part of the circuit is reconfigured. In some cases, there may also be no effect at all because this bit has no active role in the application definition. Identifying the actual effect of errors in the configuration memory is therefore

quite difficult, especially when multiple bits are simultaneously modified. Several types of design techniques can be used to make a given application more robust, but they are more limited than in the case of an ASIC design, since they have to be compatible with the existing features in the FPGA; it is for example not possible to add some sensors to detect a given kind of attacks. Achieving and validating a given security level is therefore difficult. Before using costly experimental equipments such as lasers, the designer must justify that the implemented functions are well protected against realistic errors. In most cases, the efficiency of the protection mechanisms is evaluated at design time by fault injections (either based on simulation or emulation) [1]. One of the limitations is the accuracy of the error model typically used during the injections, that may adequately represent some types of perturbations but not necessarily all types. The approach proposed in Section IV aims at overcoming this limitation. The need for specific error pattern characterization is first illustrated in Section III.

#### III. ERROR PATTERNS WITH RESPECT TO ATTACK TYPES

#### A. Results of Laser-based Attacks

One of the most efficient means for fault-based attacks is today a laser. Such equipment allows the attacker to have a very good control on the error location, both in space and time. However, several types of lasers exist and they can be used in several manners; actual attack effects depend on these attack conditions.

We will summarize here some results obtained during practical attack experiments, in order to illustrate the variability of the possible effects.

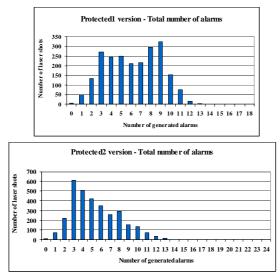

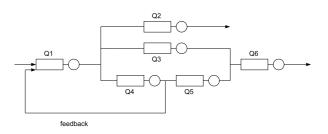

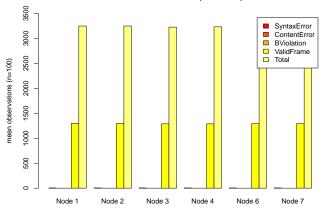

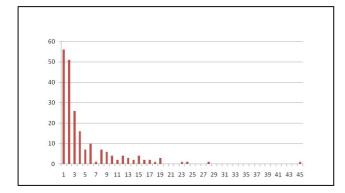

We reported in [5] an attack campaign done on an ASIC manufactured in the ST HCMOS 130 nm process, with 6 metal layers. The ASIC implemented several versions of a Montgomery multiplier for RSA acceleration, two of them with parity-based protections (Protected1 and Protected2). The laser was a pulsed Yag laser with a green output at 532 nm, 6 ns impulsions and an energy tunable from 0 to 100%, with the possibility to control the spot size. During the experiments, we used a large spot size and we only used the energy "zero" that means the lowest possible energy level, corresponding to some "leakage beam". As shown in Figure 1, this very low energy was sufficient to create many errors in the circuit as demonstrated by the number of alarm signals that were activated, each of them corresponding to a different subset of the logic. This is especially interesting because the result was obtained without any special preparation of the circuit. We just opened the package and attacked the circuit front side through the metal layers.

Similar attacks on this circuit were attempted using a much more sophisticated laser [6] part of the ATLAS platform, the pulsed laser facility of the University of Bordeaux, dedicated to laser testing and analysis of integrated circuits. We used an ultra-short pulsed laser source (1 ps) with a wavelength tunable from 780 nm to 1000 nm and microscope objectives giving adjustable spot sizes ranging from 1  $\mu$ m to 20  $\mu$ m. The available laser pulse energy on the attacked circuit is adjustable up to typically

1 nJ. In that case, it was not possible to generate errors when attacking the circuit front-side.

This case study demonstrates that (1) complex error patterns can be generated, far from the usual single bit-flip or even multiple bit-flip (MBU) models and (2) the attack effects strongly depend on the perturbation source. As a matter of fact, the most sophisticated equipment is not always the most efficient to be used in attack contexts.

Experiments have then been carried out on SRAM-based FPGAs, especially Xilinx Virtex II devices. The reason was the availability of a tool called SEFEA-ProD that allowed us to analyze in details the configuration and data errors in these devices [7]. The v1000 FPGA used in the experiments was manufactured in a 0.15 µm CMOS process, with 8 metal layers. It is encapsulated Flip-Chip and was attacked backside through the substrate. Experiments were done on the ATLAS platform [8] but also with other lasers. One of them had a wavelength near 900 nm, a power of a few Watts and several focus levels corresponding to 8 µm, 20 µm, 40 µm and 100 µm expected spot diameters [9, 10]. For the experiments reported in [9, 10], the die was thinned by a mechanical process until a residual thickness of 30 µm to ensure a good optical transmission of the light in the active layers of the device. The various experiments allowed us to draw some conclusions.

First, in most cases, a medium or large number of configuration bits are modified even after a single shot but single-bit errors can also be obtained [10].

Second, one type of bit-flip (from 1 to 0) has a much higher probability than the other. This was explained by the structure of the memory elements [10].

Figure 1. Repartition of shots with respect to the number of asserted detection bits in the protected Montgomery circuits.

Third, it was shown that in spite of multiple bit flips a non negligible percentage of errors does not affect the basic functionality. This is partly due to the unused resources in the FPGA for a given design, but also to a redundant encoding of interconnection control bits in the architecture. Finally, the detailed analysis of the modified configuration bits demonstrated noticeable differences in terms of repartition depending on the laser energy and on the spot focalization. As an example, it was shown in [9] that the slice inputs and the Hex lines were the most sensitive elements in the CLB tiles (Configuration Logic Blocks), with 70% of errors impacting such connections. However, the most sensitive element between these two was dependent on the laser spot size. With a laser spot size of 40  $\mu$ m, the probability to modify a slice input control bit was larger than the probability to flip a control bit of Hex lines. With the 8  $\mu$ m spot, the trend was opposite.

#### B. Attack Parameters and Adversary Model

Results summarized in the previous section clearly show that it is not possible to use a simple error model to represent all possible attacks. An attacker can modify several important parameters and he will use the best values to achieve his goals. The robustness of a given design must therefore be validated taking into account a given adversary model based on some knowledge about the implementation technology, on the attack equipment that is supposed to be available to the attacker and on the configuration parameters for this equipment.

When laser-based attacks are concerned, the main parameters are related to:

- Manufacturing technology, internal architecture and internal topological organization of the circuit,

- Type of laser and configuration (wavelength, energy, pulse duration, spot sizes),

- Design implementation (placement in the device).

This implies first that a real validation of the design robustness can only be done quite late in the design flow; the final placement and routing must be achieved before.

Also, the validation cannot be done without taking into account realistic error patterns for the different attack conditions. Limiting the evaluation to a generic error model (such as single bit-flips or multiple bit-flips with a given maximum multiplicity) will not be in general realistic. On the other hand, single bit-flips can occur and therefore cannot be completely neglected. Also, when multiple errors occur in the configuration, all the potential combinations of erroneous bits are not realistic since they depend on the laser parameters but also on the physical organization of the configuration bits in the FPGA array. Making multiple injections in the configuration on the basis of a random sampling is therefore not accurate even if very large multiplicity values are taken into account. A more accurate representation of possible error patterns is therefore necessary to achieve significant validation campaigns based on fault injections.

#### C. Glitch-based Attacks

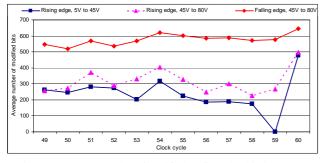

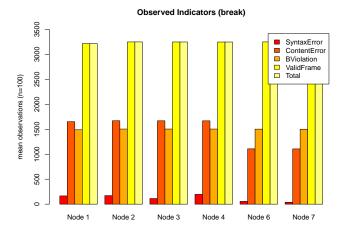

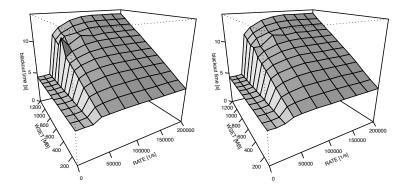

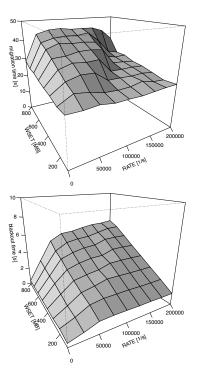

In the previous sections, we only considered laser-based attacks. Attacks can also be based on other types of perturbations, for example glitches on the power or clock signals. In general, the clock of a secured circuit is protected (e.g., by using an internal oscillator, or a digital locked loop in a FPGA) so we will focus here on glitches induced on the power lines that are more difficult to mitigate when FPGAs are used. Depending on the glitch intensity and on the occurrence time, the effects can be very different. As an example, Figure 2 [11] shows results with several intensity and polarity of glitches. The attack was made on a v1000 device running an AES encryption. The glitches were triggered either on the rising clock edge or on the falling clock edge, with intensity between 5V and 80V, during the encryption cycles 49 to 60. As illustrated in the figure, the average number of bits modified in the FPGA configuration is very large (several hundreds in most cases) and clearly depends on the injection time within the clock period [11]. In that case, injections on the falling clock edge led to about twice erroneous bits.

The need for a good adversary model, with an accurate representation of possible error patterns, is therefore also confirmed in that case.

Figure 2. Average number of modified configuration bits in a v1000 device running an AES encryption for several types of power glitch attacks.

#### IV. METHODOLOGY OVERVIEW

#### A. Fault injection techniques

Several approaches have been used to evaluate at design time the dependability level of a circuit. We will focus here on approaches able to inject errors in both user flip-flops and configuration memories for SRAM-based FPGAs. In that case, simulation techniques are in general not adequate because there are almost no simulation models available including the configuration memory of commercial devices.

One approach proposed to perform fault injection campaigns is based on partial reconfiguration of a circuit prototype implemented on a SRAM-based FPGA [12-13]. The approach was primarily developed to inject transient errors in the user logic but had the potential to study the effect of errors in the configuration memory as well. The control of the reconfiguration was made by a host PC connected to the FPGA board. In [14], the authors proposed to control the partial reconfiguration by a program executed on an embedded processor. Such an "endo-reconfiguration" has the advantage to considerably reduce the number of data to be exchanged between the FPGA component and the host PC, thus accelerating the fault injection process. The approach is made possible by using the ICAP interface (Internal Configuration Access Port) provided by Xilinx for the Virtex FPGAs. Only SEUs (Single Event Upsets i.e., single bit-flips) were considered. Run-time reconfigurability

is also used in [15] to inject faults in Look-Up Tables (LUTs) and in user flip-flops. An approach similar to [14] is presented in [16] but takes into account some multiple and cumulative bit errors. In addition, the environment can perform error propagation analyses, but restricted to specific fault detection or tolerance features. In [17], the FLIPPER platform is introduced to emulate SEU-like faults. Partial reconfiguration is again used but on a more complex platform composed of a main board and a daughter board with the FPGA under test. Complex dedicated hardware is therefore necessary. Similarly, dedicated hardware is required by FT-UNSHADES-C [18]. In addition, although this environment uses partial reconfiguration, it also requires implementing two copies of the system under test, one being used for a golden reference. The first consequence is of course to severely limit the complexity of the system that can be evaluated on a given device. The second consequence is that it is in general not possible to have the same placement and routing of the system during the evaluation and in the final product. Since the consequence of a given bit-flip strongly depends on the placement and routing of the design, such an approach is often too intrusive to give significant results. By comparison, using the ICAP interface only requires a small part of the device logic. With a guided placement and routing, it is often possible to avoid any change in the design implementation.

A few other approaches have been reported. On-the-fly modification of the configuration bitstream of XC4000 FPGAs, during reconfiguration, by some logic on the board was proposed in [19] but requires additional board-level modifications. The approach used in [20] focused on the logic used to reconfigure the FPGA component.

In the sequel, we will give results on a platform developed using the ICAP interface, but the methodology may be adapted on other types of fault injection platforms.

## B. Virtual Fault-based Attacks on SRAM-based FPGAs

In general, fault injection campaigns are performed on the basis of a given error model, most often the SEU model implying one bit flip at a time in a circuit. In some cases, multiple bit errors are considered, assuming a given multiplicity value and a random distribution. However, as previously explained, such models do not represent well some perturbation conditions and they are unable to accurately take into account the actual layout and sensitivity of the elements in a chip or the physical characteristics of the perturbation source. Such models may therefore lead to large errors on the robustness quantitative evaluations.

Our goal is therefore to inject more realistic patterns, based on previous pre-characterization of the technological target. This pre-characterization can be done once for a given device and a given perturbation source (e.g., some particle flux, some electromagnetic fields or some type of laser with a given focus and a given energy). It can be done statically on the idle circuit, if possible using a device configuration that covers most of the possible configuration patterns for the CLBs and embedded memory blocks. It can also be done dynamically on the circuit running a given application. In the later case, results can be more precise with respect to this application but can induce some bias if the analysis has finally to be done for a different application.

The actual error patterns obtained during this device precharacterization are recorded and analyzed, e.g., with a tool like SEFEA-ProD [7], indicating all erroneous bits obtained in a bitstream after readback. Then the absolute values of the erroneous bits for each recorded error pattern are abstracted in order to obtain error coordinates that are relative to a CLB.

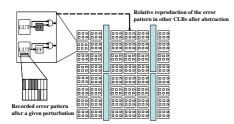

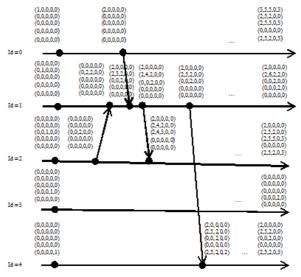

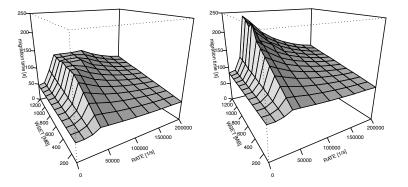

The abstracted relative coordinates are stored in a database that is then used during the fault injection campaigns performed at design time using partial reconfiguration, without resorting again to the physical perturbation source. Each relative error pattern in the database can be relocated i.e., injected into any CLB (or memory block) used in the device for a given design and at any clock cycle during the application execution for dynamic robustness evaluations. Of course, this relocation is only possible thanks to the regularity and repeatability of a FPGA structure. Another advantage of this regularity, in the case of laser-based pre-characterizations, is that only a small representative part of the device has to be scanned; the effects induced in the whole CLB matrix can then be inferred. This can noticeably reduce the laser availability requirements for the device pre-characterization. The relocation process is illustrated in Figure 3.

Figure 3. Illustration of error pattern relocation.

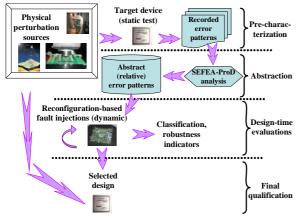

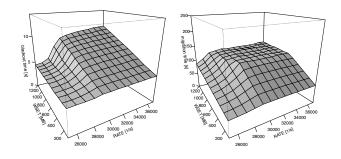

Figure 4. Global robustness evaluation flow.

Using the generated database, the same campaign can easily be run on several versions of a design in order to compare several implementations or several protection schemes. Furthermore, the consequence of any pattern obtained once in the device during the pre-characterization can be assessed at any position in the whole device and at any time. Let us notice that this would not be possible for example under a particle beam (for natural perturbations) due to the random distribution and the usually small number of events obtained during a given beam slot. A more comprehensive and realistic robustness analysis can thus be achieved at low cost with our methodology. The global flow is summarized in Figure 4.

#### C. Virtual Fault-based Attacks on ASICs or some FPGAs

For FPGAs with permanent or error-immune configurations, the same methodology can be applied but limited to errors in the user flip-flops.

In the case of ASICs (or any masked circuits) the relocation principle presented in the previous section is in general not applicable. However, the same concept can be used for regular circuits (parallel architectures, multi-cores ...), limited to the repetitive structures.

Another possible use concerns the evaluation of software-related robustness. In the case of a microprocessor (or DSP), for example, the pre-characterization allows recording possible error patterns within the processor core. It is then possible to use the proposed approach to evaluate offbeam the effect on robustness of software modifications, provided a synthesizable model (or a very accurate simulation model) exists for the microprocessor. A processor prototype can be implemented on the FPGA and only error patterns in user flip-flops are injected.

#### V. IMPLEMENTED FRAMEWORK AND RESULTS

Our environment is implemented on a Virtex II-Pro component, using one of the embedded PowerPC processors to manage the fault injection campaign and the ICAP IP to perform the partial endo-reconfiguration. This environment is easily portable to other Virtex families. It allows the injection of any single- or multiple-bit error in the configuration and in the user flip-flops of the Configuration Logic Blocks (CLBs). The fault injection can be triggered at any time during the execution of an application onto the FPGA. The originality of the platform lies in the database we added to store the realistic error patterns, as presented in the previous section.

The methodology has been applied in the case of the Leon2 microprocessor, implemented on a Virtex II Pro device, and running several program examples chosen to be representative of several application areas: Fir is a FIR filter, Mtmx is a matrix multiplication, Sieve is a computation of prime numbers with the Sieve of Eratosthenes and AES is a standard encryption/decryption function. The results illustrate the impact of realistic error patterns compared to the most used model in the literature i.e., single bit-flips in the user flip-flops. The relative error patterns were derived from previous experiments [9]. The database included 5435 error patterns. Each pattern involved between 1 and 41 erroneous configuration bits, with an average of 11.7 bits per pattern. A single pattern can involve bits in several LUTs (from 1 to 6 LUTs in the patterns used for the experiments, 1.7 on an average). For each program, we have injected the relative error patterns in the CLBs used to implement the

Leon2 integer pipeline. We used statistical fault injection and the number of randomly selected injection time and location was chosen so that the margin of error on the classification results is 5% with 95% confidence. The number of injections performed for a given pipeline stage and a given program ranges from 8,000 to 160,000. The injected error patterns were classified, based on the system behavior after the injection, as "Silent" (no effect on the application results), "Error" (wrong result but the system is still alive and can perform other computations), "Failure" (wrong program termination, unexpected behavior, uncertain future behavior) or "Crash" (fully unrecoverable error and system behavior, until reset). The results are summarized in Table I for errors globally injected in the five pipeline stages. They clearly show that realistic error patterns lead to much more application failures. So an evaluation based on single bitflips noticeably under-estimates the failure probability and is not acceptable for security analyses.

|                | Silent                                                                           | Error                                                                                                                                                                                                                                      | Failure                                                                                                                                                                                                                                                                                                                                   | Crash                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEU FF         | 54.61%                                                                           | 11.63%                                                                                                                                                                                                                                     | 10.88%                                                                                                                                                                                                                                                                                                                                    | 22.89%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Error patterns | 3.40%                                                                            | 0.98%                                                                                                                                                                                                                                      | 60.54%                                                                                                                                                                                                                                                                                                                                    | 35.08%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SEU FF         | 52.59%                                                                           | 12.03%                                                                                                                                                                                                                                     | 14.55%                                                                                                                                                                                                                                                                                                                                    | 20.83%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Error patterns | 7.61%                                                                            | 0%                                                                                                                                                                                                                                         | 31.67%                                                                                                                                                                                                                                                                                                                                    | 60.72%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SEU FF         | 47.77%                                                                           | 12.11%                                                                                                                                                                                                                                     | 23.46%                                                                                                                                                                                                                                                                                                                                    | 16.66%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Error patterns | 4.90%                                                                            | 0%                                                                                                                                                                                                                                         | 40.08%                                                                                                                                                                                                                                                                                                                                    | 55.02%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SEU FF         | 57.96%                                                                           | 8.52%                                                                                                                                                                                                                                      | 24.67%                                                                                                                                                                                                                                                                                                                                    | 8.85%                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Error patterns | 18.41%                                                                           | 0.52%                                                                                                                                                                                                                                      | 44.21%                                                                                                                                                                                                                                                                                                                                    | 36.85%                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | Error patterns<br>SEU FF<br>Error patterns<br>SEU FF<br>Error patterns<br>SEU FF | SEU FF         54.61%           Error patterns         3.40%           SEU FF         52.59%           Error patterns         7.61%           SEU FF         47.77%           Error patterns         4.90%           SEU FF         57.96% | SEU FF         54.61%         11.63%           Error patterns         3.40%         0.98%           SEU FF         52.59%         12.03%           Error patterns         7.61%         0%           SEU FF         47.77%         12.11%           Error patterns         4.90%         0%           SEU FF         57.96%         8.52% | SEU FF         54.61%         11.63%         10.88%           Error patterns         3.40%         0.98%         60.54%           SEU FF         52.59%         12.03%         14.55%           Error patterns         7.61%         0%         31.67%           SEU FF         47.77%         12.11%         23.46%           Error patterns         4.90%         0%         40.08%           SEU FF         57.96%         8.52%         24.67% |

Silent

From

Failure

Crash

#### VI. CONCLUSION

Results shown in this paper demonstrate that classical fault injection campaigns based on single bit-flips noticeably overestimate the robustness of a design, at least for the type of perturbation considered here. The proposed methodology leads to more accurate robustness evaluations, with a minimum use of costly equipments since precharacterization is done only once for a given device and a given perturbation source.

In this paper, we focused on malicious attacks because error patterns are in general more complex than those obtained under natural conditions. However, the same strategy can be used on the basis of a few events obtained for example under a particle beam, to take advantage of regular structures and increase the confidence in robustness. This approach will be used in further work to evaluate the efficiency of error mitigation techniques.

#### REFERENCES

R. Leveugle, "Early analysis of fault-based attack effects in secure circuits", IEEE Transactions on Computers, vol. 56, no. 10, October 2007, pp. 1431-1434

- [2] A. K. Lenstra, "Memo On RSA Signature Generation In The Presence Of Faults", private communication (available from the author), September 28, 1996.

- [3] R. Anderson and M. Kuhn., "Low Cost Attacks on Tamper Resistant Devices", 5th International Workshop on Security Protocols (IWSP), 1997, LNCS 1361, Springer-Verlag, pp. 125-136

- [4] J. Blömer and J.-P. Seifert, "Fault based cryptanalysis of the AES", e-Print Archive of the IACR, 2002, <u>http://www.iacr.org/</u>.

- [5] R. Leveugle et al., "Experimental evaluation of protections against laser-induced faults and consequences on fault modelling", Design, Automation and Test in Europe Conference (DATE), April 16-20, 2007, pp. 1587-1592

- [6] V. Pouget, D. Wan, P. Jaulent, A. Douin, D. Lewis, and P. Fouillat, "Recent developments for SEE testing at the ATLAS laser facility", Proc. of 15th Single-Event Effects Symposium, 2006

- [7] V. Maingot, J. B. Ferron, R. Leveugle, V. Pouget, and A. Douin, "Configuration errors analysis in SRAM-based FPGAs: software tool and practical results", Microelectronics Reliability, Elsevier, vol. 47, no. 9-11, September-November 2007, pp. 1836-1840

- [8] V. Pouget et al., "Tools and methodology development for pulsed laser fault injection in SRAM-based FPGAs", 8th Latin-American Test Workshop (LATW), March 12-14, 2007, pp. 167-172

- [9] G. Canivet et al., "Detailed analyses of single laser shot effects in the configuration of a Virtex-II FPGA", 14th IEEE International On-Line Testing symposium, Rhodes, Greece, July 6-9, 2008, pp. 289-294

- [10] G. Canivet et al., "Characterization of effective laser spots during attacks in the configuration of a Virtex-II FPGA", 27th IEEE VLSI Test Symposium (VTS'09), May 3-7, 2009, pp. 327-332

- [11] G. Canivet, "Analyse et conception sécurisée de plates-formes reconfigurables", PhD thesis, Grenoble INP, Grenoble, France, September 2009 (in French).

- [12] L. Antoni, R. Leveugle, and B. Fehér, "Using run-time reconfiguration for fault injection in hardware prototypes", IEEE Int. Symposium on Defect and Fault Tolerance in VLSI Systems, 2000, pp. 405-413

- [13] L. Antoni, R. Leveugle, and B. Fehér, "Using run-time reconfiguration for fault injection applications", IEEE Transactions on Instrumentation and Measurement, vol. 52, no. 5, October 2003, pp. 1468-1473

- [14] L. Sterpone and M. Violante, "A new partial reconfiguration-based fault-injection system to evaluate SEU effects in SRAM-based FPGAs", IEEE Transactions on Nuclear Science, vol. 54, issue 4, part 2, August 2007, pp. 965-970

- [15] P. Kenterlis et al., "A low-cost SEU fault emulation platform for SRAM-based FPGAs", 12th IEEE International On-Line Testing symposium, Como, Italy, July 10-12, 2006, pp. 235-241

- [16] C. Bolchini, F. Castro, and A. Miele, "A fault analysis and classifier framework for reliability-aware SRAM-based FPGA systems", 24th IEEE Int. Symposium on Defect and Fault Tolerance in VLSI Systems, Chicago, IL, USA, October 7-9, 2009, pp. 173-181

- [17] M. Alderighi et al., "Evaluation of single upset mitigation schemes for SRAM bassed FPGAs using the FLIPPER fault injection platform", 22nd IEEE Int. Symposium on Defect and Fault Tolerance in VLSI Systems, Rome, Italy, September 26-28, 2007, pp. 105-113

- [18] L. Sterpone, M. A. Aguirre, J. N. Tombs, and H. Guzmán-Miranda, "On the design of tunable fault tolerant circuits on SRAM-based FPGAs for safety critical applications", Conference on Design, automation and test in Europe (DATE), 2008, pp. 336-341

- [19] M. Alderighi et al., "A fault injection tool for SRAM-based FPGAs", 9th IEEE International On-Line Testing symposium, Kos, Greece, July 7-9, 2003, pp. 129-133

- [20] M. Alderighi et al., "A tool for injecting SEU-like faults into the configuration control mechanism of Xilinx Virtex FPGAs", 18th IEEE Int. Symposium on Defect and Fault Tolerance in VLSI Systems, November 3-5, 2003, pp. 71-78

## On Time, Conflict, Weighting and Dependency Aspects of Assessing the Trustworthiness of Digital Records

Jianqiang  $Ma^{\ast \dagger},$  Habtamu Abie $^{\dagger},$  Torbjørn Skramstad\* and Mads Nygård\*

\* Department of Computer and Information Science Norwegian University of Science and Technology, Trondheim, Norway Email: {majian, torbjorn, mads}@idi.ntnu.no <sup>†</sup> Norwegian Computing Center, Oslo, Norway Email: {Jianqiang.Ma, Habtamu.Abie}@nr.no

Abstract-In the area of digital records management, the reliability of a digital record's operator varies over time, and consequently affects the trustworthiness of the record. The quality of the reliability of the operator is a measure of the quality of the record's evidential value that is, in turn, a measure of the record's trustworthiness. In assessing the trustworthiness of a record using evidential value, it is essential to combine evidence from various sources, which may be conflicting and/or interdependent. In this paper we describe our research on these problems, and develop a trustworthiness assessment model which addresses these problems and integrates a beta reputation system in combination with a forgetting factor to assess the temporal aspects of the evidential value of an operator, a weighting mechanism to detect and avoid conflicts, and a weighted sum mechanism to combine dependent evidence. Our results show that the integrated model can improve the objective assessment of the trustworthiness of digital records over time using evidential value as a measure of trustworthiness.

## Keywords-Trustworthiness Assessment, Trust, Digital Record Management.

#### I. INTRODUCTION

In the area of digital records management, research on the trustworthiness of digital records is an issue that has received much attention mainly in two areas, Security [1], [2] and Trustworthy Repositories [3], [4]. In our previous work [5], we proposed a complementary method, which assesses the trustworthiness of digital records based on their evidential values using the Dempster-Shafer (D-S) theory of evidence [6]. Four challenges to the assessment model have been identified, i.e., time, conflict, weighting, and dependency aspects. In this paper, we improve our previous model by addressing all four aspects.

This paper describes the time aspect of the trustworthiness assessment model using the reliability of a digital record's operator, since the reliability of an operator varies over time, and, which in turn, affects the assessment result of the trustworthiness of the digital record. Inspired by [7], historical information about the behaviours of operators, which can be obtained from the logs of digital repositories, is used to evaluate their reliability. Correct or incorrect behaviours of operators can be recognised as positive or negative ratings of their reliability. In this way, the widelyresearched reputation system mechanism [8]–[10] can be used here for the evaluation of operators' reliability. In this paper, we adopt the beta reputation system [8] to evaluate the reliability of operators, and to create a function to map the evaluated result to the mass function, which can later be used in the D-S theory for the assessment of the trustworthiness of digital records.

Many researchers have criticized the way conflicts are handled in the D-S theory [11], [12]. When using the D-S theory to combine evidential values of evidence around digital records, we have paid attention to these criticisms. We first investigate how to detect conflicts between evidence, and then avoid those conflicts by assigning different weighting, since different evidence may have different importance to the assessment. In addition, we study the combination of evidential values from interrelated evidence, since Dempster's rule of combination is based on independent evidence. We use an alternative approach to combine evidential values from dependent evidence.

As the time aspect deals with evidential values assigned to records' operators, and the other three aspects deal with the combination of evidential values, these four aspects together improve the assessment model by increasing the quality of the evidential values assigned to the evidence, and by improving the way they are combined.

We note that the investigation and evaluation of operators' reliability over time is not fundamentally different from research in the domain of reputation systems [8]. The applicability to the area of trustworthiness assessment of digital records and the integration with the D-S theory are two of the main contributions of this paper. The third is the integration of a conflict detection mechanism, a weighting mechanism, and a dependent evidence combination mechanism in the D-S theory for assessing the trustworthiness of digital records.

The rest of this paper is organised as follows. Section II describes the related work. Section III briefly introduces the Trustworthiness Assessment Model proposed in our previous work. Section IV, V, VI, and VII give an account of our research on the temporal, conflict, weighting and

dependency aspects of the trustworthiness assessment model, respectively. Finally, the conclusion and future work are presented in Section VIII.

## II. RELATED WORK

Reputation systems allow users to rate on an agent that they have had a transaction with, and use these ratings to assess the reliability of the agent. It was first used in online shopping websites, such as eBay, to assess the trustworthiness of online sellers [13], and was later further developed in the Peer-to-Peer (P2P) networks area to assess the reliability of agents [9], [10]. An extensive survey and overview of trust and reputation systems can be found in [14]. Among these reputation systems, the beta reputation system together with a forgetting factor proposed by Jøsang [8] is capable of assessing one's reliability at a particular time, based on historical information. It has been adopted in many areas [15]. In this paper, we adopt the beta reputation system to evaluate the reliability of records' operators in the trustworthiness assessment model because of its "flexibility and simplicity as well as its foundation on the theory of statistics". The beta reputation system was presented as a stand-alone mechanism in [8]. By mapping the evaluation results to the basic belief assignments (bbas), we integrate it with the D-S theory for the assessment of the trustworthiness of digital records.

The D-S theory of evidence has been applied in many different areas to combine evidence from different sources [16], [17]. One feature of the D-S theory that has received criticisms is its way of handling conflicts [11], [12]. Many alternatives to Dempster's rule of combination have been proposed. The most famous alternatives are conjunctive [18], disjunctive [19] and Yager's [20] combination rules. In the area of belief conflict detection, Josselme et al. [21] proposed a method for measuring the distance between two bbas. Liu [22], however, argued that by only using this distance one cannot distinguish whether two bbas are in conflict or not. Consequently, after formally defining the conflict between two bbas, the author proposed an approach to analyse conflicts, which uses the mass of the combined belief allocated to the empty set before normalisation and the distance between betting commitments (see Section V). Our method of detecting possible conflicts is similar to this method. It differs from it in that our method resolves these conflicts by assigning different weighting to the sources.

Regarding the dependency aspect of different sources, Ferson et al. [23] have done a thorough analysis of dependencies in the D-S theory and probabilistic modelling, including copulas and Fréchet bounds. The weighted sum operator was proposed by McClean and Scotney [16] for the integration of distributed databases. They proved that "the weighted sum operator is a mass function and it is both commutative and associative". It was later adopted by Hong et al. [17] to combine bbas of dependent sensor data in smart homes. They assigned equal weight to the dependent sensors. However, this might not be true in most cases. In this research, we integrate the weighted sum operator into our assessment model to solve the dependency problem by assigning different weighting to sources based on their importance to the assessment.

## III. THE TRUSTWORTHINESS ASSESSMENT MODEL

In this section, we briefly introduce the model for the assessment of the trustworthiness of digital records in order to improve the understanding of the aspects addressed in this paper. For detail information about the model, readers are referred to our previous paper [5].

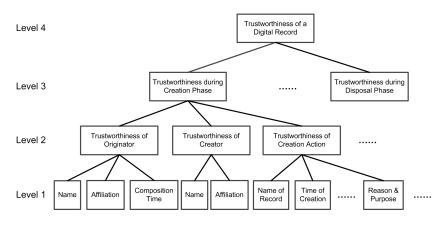

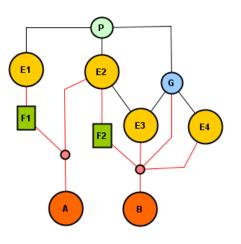

In order to assess the trustworthiness of digital records, we have identified, analysed and specified a list of evidence that shall be stored in the metadata related to digital records [24]. These metadata, named Evidence-Keeping Metadata (EKM), are a subset of the Record-Keeping Metadata [25], but limited only to the metadata, which contain evidence of the trustworthiness or untrustworthiness of digital records. A digital record associated with its EKM can be structured as a tree based on a proposed record's life-cycle model [24].

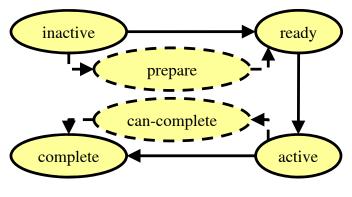

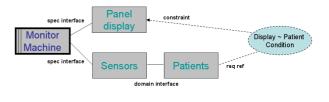

As shown in Fig. 1, the trustworthiness of a digital record is built up of trustworthiness during different phases of the record's life cycle, which in turn can be categorised by the trustworthiness of various components. Finally, the trustworthiness of each component is assessed using evidence stored in EKM. After receiving the linguistic evidential values of EKM as well as their "trustworthiness hypotheses" (either trustworthy or untrustworthy) from a panel of experts, the assessment model maps them into bbas, and uses these bbas in the D-S theory to assess the trustworthiness of a digital record from the bottom to the top.

In [5], we have proposed this model and identified a number of challenges that still need to be met, to wit the temporal aspect, conflicts, dependencies, and weighted differences among EKM. In the ensuing sections, we describe these challenges, respectively. Note that the model uses bbas assigned to the EKM as basic units for the assessment of the trustworthiness of digital records. Hence, as long as the solutions to these challenges can be mapped to bbas, it is fairly easy to integrate the solutions into the trustworthiness assessment model.

#### IV. TEMPORAL ASPECT

In this section, we describe the temporal aspect of the trustworthiness assessment model briefly introduced above. Inspired by [7], we studied the temporal aspect by looking into the reliability changes of digital records' operators over time. Using long-term observations, the history of digital records as well as the behaviours of records' operators can be logged. On the basis of that historical information, the behavioural patterns of the operators can be learnt, which

Figure 1. Structure of the EKM for the assessment of the trustworthiness of a digital record [24]

provide us with the possibility to evaluate the reliability of the operators' operations on the records.

Good and bad behaviours of an operator P can be documented and used to learn his/her behavioural pattern. A good behaviour means that the operation on a digital record does not compromise the trustworthiness of the record. While a bad behaviour means that the operation decreases the trustworthiness of the record. Good or bad behaviours of P can be discovered through verifications performed by one or more other operators or by verification software. The way of detecting good or bad behaviours in a digital library system is outside the scope of this paper. Instead, this paper focuses on how to learn P's behavioural patterns.

The reliability of P can be predicted using the numbers of good and bad behaviours. It can further be interpreted as the evidential value of P, because both reliability and evidential value present the degree to which P can be used as evidence to prove the trustworthiness of the record Poperated on. The reliability - evidential value - of P varies along with the accumulation of the number of behaviours. In this study, the beta reputation system [8] is adopted to assess the reliability - evidential value - of P.

In our case, we map a good behaviour of P to a good feedback on P, and a bad behaviour to a bad feedback. Thus, the evidential value of P can be calculated as:

$$EV(P) = \frac{g+1}{g+b+2} \tag{1}$$

with the restriction that  $g, b \ge 0$ , where g is the number of good behaviours that have been exhibited by P, and b is the number of bad behaviours that have been exhibited by P.

In order to integrate the evaluated evidential value of P into the trustworthiness assessment model and combine it with evidential values of other EKM, EV(P) needs to be mapped to the bbas defined in the D-S theory. In addition, a "trustworthiness hypothesis"  $H_P \in \{true, false\}$  should be specified, where  $H_P = true$  or  $H_P = false$  mean that P (presented as "Name" of operator in Fig. 1, e.g., "Name of

Creator"), as evidence, can be used to prove that *P*'s higher level node is either trustworthy or untrustworthy.

When P exhibits more good behaviours than bad behaviours (g > b), it shows that P tends to be reliable, and should be used to prove that its higher level node is trustworthy to a certain degree, thus,  $H_P = true$ , and vice versa. In the case when g = b,  $H_P = \phi$ , which means that it cannot prove its higher level node is either trustworthy or untrustworthy. When  $H_P = false$ , instead of using  $\frac{g+1}{g+b+2}$ , the evidential value of P is assigned as  $EV'(P) = 1 - \frac{g+1}{g+b+2} = \frac{b+1}{g+b+2}$ , since in this case, it is used to present the degree of its higher level node's untrustworthiness.

It is obvious that both EV(P) and EV'(P) are in the interval [0.5, 1]. Since bba is in the interval [0, 1], it is necessary to scale EV(P) and EV'(P) into that interval. Hence, the mapping rules are defined as follows:

if

$$g > b$$

, then  $H_P = true$  and

$$\begin{cases} m_P(T) = \frac{2g+2}{g+b+2} \\ m_P(\overline{T}) = 0 \\ m_P(U) = \frac{g-b}{g+b+2} \end{cases}$$

(2)

if

$$g < b$$

, then  $H_P = false$  and

$$\begin{cases} m_P(T) = 0\\ m_P(\overline{T}) = \frac{2b+2}{g+b+2}\\ m_P(U) = \frac{b-g}{g+b+2} \end{cases}$$

(3)

if

$$g = b$$

, then  $H_P = \phi$  and

$$\begin{cases} m_P(T) = 0\\ m_P(\overline{T}) = 0\\ m_P(U) = 1 \end{cases}$$

(4)

where  $g, b \ge 0$  are the numbers of good or bad behaviours of P, as defined in Equation (1).

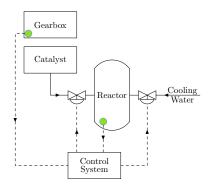

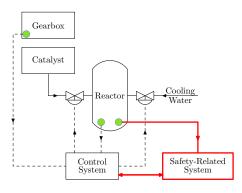

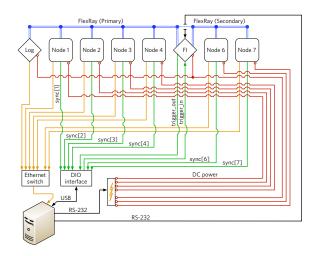

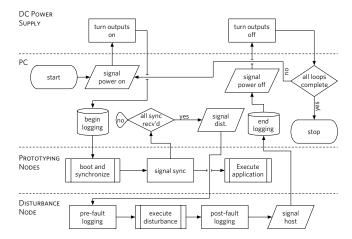

As presented in Equation (1), the evidential value of P changes with the accumulation of good or bad behaviours. However, from the long-term perspective, the old behaviours may be less relevant in the revelation of P's evidential value, because the behavioural pattern of P might have changed. Therefore, we introduce the forgetting factor  $\delta$  proposed in [8] into the calculation in order to reduce the impact of the old behaviours on modelling of P's current behavioural pattern. That is, exhibiting G good behaviours at an older time  $t_1$  equals exhibiting  $G\delta^{t_2-t_1}$  good behaviours at a more recent time  $t_2$ , where  $t_2 > t_1$  and  $0 \le \delta \le 1$ . When  $\delta = 0$ , it forgets every old behaviours, and uses the most recent behaviour to calculate the evidential value of P. In other words, the old behaviours have no impact on the calculation at all. When  $\delta = 1$ , it never forgets, and the old behaviours have the same impact as the recent behaviours on the calculation of the evidential value of P.